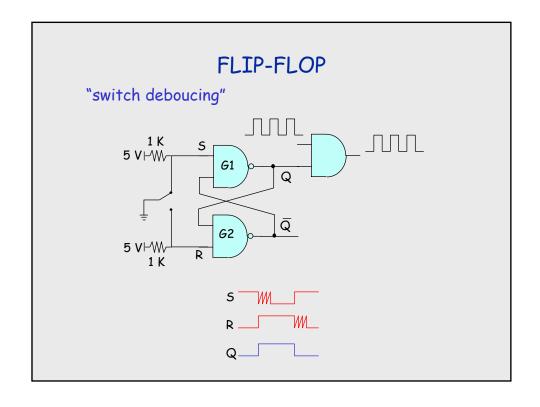

- · dispositivo com memória

- · uso em contadores, acumuladores, latches

| NAND |                |  |  |

|------|----------------|--|--|

| В    | Q              |  |  |

| 0    | 1              |  |  |

| 0    | 1              |  |  |

| 1    | 1              |  |  |

| 1    | 0              |  |  |

|      | <b>B</b> 0 0 1 |  |  |

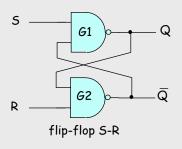

| 5 | R | Q | Q |

|---|---|---|---|

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   |   |   |   |

(dois estados estáveis) indeterminado

- se S = 0 e R = 1, então Q = 1 e  $\overline{Q} = 0$

- · se 5 mudar de estado, as saídas não se alteram

- se S = 1 e R = 1, então Q = 1 e  $\overline{Q} = 0$

- · se R mudar de estado, as saídas se alteram

- se S = 1 e R = 0, então Q = 0 e  $\overline{Q} = 1$

| NAND |   |   |  |

|------|---|---|--|

| Α    | В | Q |  |

| 0    | 0 | 1 |  |

| 1    | 0 | 1 |  |

| 0    | 1 | 1 |  |

| 1    | 1 | 0 |  |

|      |   |   |  |

| 5 | R | $Q_{n+1}$ |

|---|---|-----------|

| 0 | 0 | $Q_n$     |

| 0 | 1 | 0         |

| 1 | 0 | 1         |

| 1 | 1 | ?         |

|   |   |           |

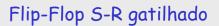

- os sinais lógicos das entradas S e R estão bloqueados enquanto o clock estiver em nível baixo (LO)

- os sinais serão transferidos ao flip-flop quando o clock estiver em nível alto (HI)

- · S e R podem ser entradas de dados

## Flip-Flop Mestre-Escravo sensível à transição

- · possui dois flip-flops (mestre e escravo)

- enquanto o clock estiver HI ou LO:

- saída do flip-flop mestre igual à entrada

- entrada do flip-flop escravo está desabilitada

- · na transição do clock (HI-LO ou LO-HI)

- mestre é desconectado da entrada

- saída do mestre é transferida para a entrada do escravo

# Flip-Flop Mestre-Escravo sensível à transição

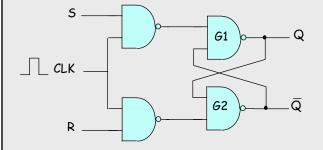

#### • flip-flop JK:

| CLK        | S | R | J | K | $Q_{n+1}$ |

|------------|---|---|---|---|-----------|

| $\uparrow$ | 0 | 0 | 0 | 0 | Q         |

| $\uparrow$ | 0 | 0 | 0 | 1 | 0         |

| $\uparrow$ | 0 | 0 | 1 | 0 | 1         |

| $\uparrow$ | 0 | 0 | 1 | 1 | Q         |

| -          | 0 | 1 | - | - | 0         |

| -          | 1 | 0 | - | - | 1         |

#### · flip-flop D:

| CLK          | D | S | R | Q | Q |

|--------------|---|---|---|---|---|

| 1            | 0 | 0 | 0 | 0 | 1 |

| <b>↑</b>     | 1 | 0 | 0 | 1 | 0 |

| $\downarrow$ | - | 0 | 0 | Q | Q |

| -            | - | 1 | 0 | 1 | 0 |

| -            | - | 0 | 1 | 0 | 1 |

| -            | - | 1 | 1 | 1 | 1 |

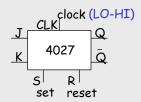

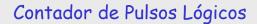

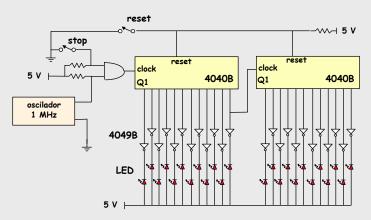

### Contador de 12 bits (4040B)

- uma entrada (clock input); 12 saídas paralelas (0 4095)

- · sensível à transição HI-LO (incrementa uma unidade)

- reset = 1, saídas Q<sub>n</sub> = 0

- · pode ser usado como um divisor:

- Q1 divide por 2; Q2 divide por 4; Q12 divide por 4096

- · contador de 24 bits (~ 16 milhões)

- reset = 1, saídas Q<sub>n</sub> = 0

- · 4049B é um buffer que fornece corrente (5 mA) para acender os LED's

- contagem é iniciada/parada através da chave que habilita/desabilita a porta AND, ligada ao clock

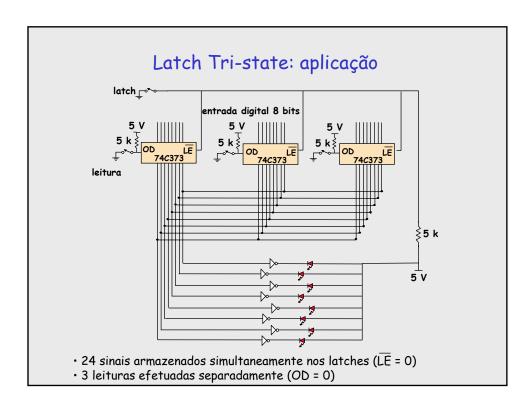

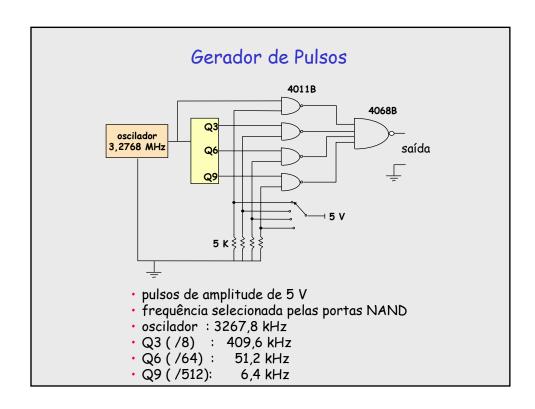

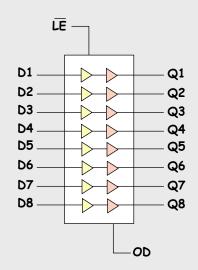

#### Latch Tri-state

- · importante na transmissão de sinais digitais do e para o PC

- latch pode armazenar ("trancar") um dado, enquanto sua saída estiver em alta impedância (tri-state)

- conexão de várias entradas/saídas em um mesmo barramento de dados (bus)

- Q = D, quando  $\overline{LE}$  = 1 (transparente)

- quando LE = 0, Q mantem seu nível lógico, independente do estado de D

### Latch Tri-state

- JL em LE, dados D<sub>n</sub> armazenados no latch na transição HI-LO

- OD = 1, tri-sate

- OD = 0, dados apresentados nas saídas Q<sub>n</sub>